# PERFORMANCE AND AREA OVERHEAD OPTIMIZATION OF NETWORK-ON-CHIP ARCHITECTURE USING RECONFIGURABLE SWAPPING ROUTER TECHNIQUE

M.Thamarai Selvan<sup>1</sup>, Dr.N.Pasupathy<sup>2</sup>

<sup>1</sup>Research scholar, Department of Electronics, Erode Arts and Science College, Erode, India, <sup>2</sup>Associate professor, Department of Electronics, Erode Arts and Science College, Erode, India,

### Abstract

At present scenario transistor scaling uses step by step complex automatic plans to optimize integrated chip (IC) design. The expansive variety of transistors on hand today empowers the development of chip multiprocessors that contain several on-chips interconnects. For an instance network onchip (NoCs), have turned out to be significant mainstream and information in the network during end to end transmission depends on congestion control. Though several algorithms focused on network congestion we have concentrate on optimizing buffer through reconfigurable architecture. Though larger buffer improve the performance of the architecture which in turn consumes more area and delay. In this paper we recommend the utilization of a , switch, where the aid openings are powerfully distributed to construct switch productiveness in a NoC, even beneath as an alternative particular correspondence loads. In the proposed method, the profundity of every guide phrase utilized as part of the input channels of the switches can be reconfigured at run time. The reconfigurable transfer lets the proposed swapping method outperforms existing reconfigurable router design in terms of area overhead and timing constrain.

Key words:NoC, integrated chip, reconfigurable swapping router,SoC.

### I. Introduction:

At present trends ultra low power system on chip(SoCs) are rising as one of the technique to assist the developing a firm networks, considering that they provide processor designs adjusted to selected difficulty in transferring data , related to programming flexibility. To guarantee flexibility and execution, future SoCs will consolidate a few varieties of processor nodes of widely particular sizes, prompting an exceedingly heterogeneous architecture. The expanding interconnection multifaceted nature and the recognized adaptability deficiency of transports require any other version of among affiliation. The correspondence amongst centers of a SoC having reusable and flexible interconnections is being given by structures onchip (NoCs) [1]. NoCs were proposed to coordinate a few Intellectual Property (IP) facilities, giving excessive correspondence transmission ability and parallelism. [2] In this paper an essential to find an technique to maintain the off-bypass on statistics transmission realistic in framework models with tradeoffs amongst cost factor, power, and execution is considered. Also, in an equipment setting, the framework must offer flexibility with hightransmission potential, low-area utilization, and energy-efficiency. Interconnection texture allows centers to get to memory, speak with each other and with some thing remains of the framework. [3] this paper specific that to make sure the growth in execution of widely useful CPUs, one wishes to utilize massive parallel processing. For this, extra free CPUs, extra self sustaining memory controllers were utilized, and it's far possible to find numerous applications that usage heterogeneous processors with a few controllers to vast memory interface. One can find a case of such engineering on the Xbox360 [4].

[5] In this paper, The reconfigurable switch show how a NoC worked with reconfigurable switches lets in the utilization of resources in a network. A NoC using a fixed estimate switch, the remaining demonstrating a big support profundity and inflicting higher power scattering .Our particular method goes for furnishing the switch with а selected measure of reconfiguration motive, allowing modifications inside the degree of support utilization in every data channel, in correspondence with routing architecture. At the point the attention to giving a reconfigurable switch that can improve manage and decorate power usage while supporting the correspondence design.

### **II.Contribution:**

In this paper, we show reconfigurable swapping routing protocols, a dependable solution for structures on-chip topologies. This proposed swapping use a reconfigurable switch layout to reduce the over architectural complexity. In the First stage, it reconfigures singular switches with a unique and flexible NoC transfer layout. Second, a unique rerouting arrangement that modifies the correspondence ways to keep away from the all the routing hub. This framework based on silicon substrates, where as error detection and correction methodologies are inbuilt to check the possibility of fault occurs during transmission. Additionally, this paper is taken care of out as takes after. Section I exhibits preamble of the problem and identifies low efficiency in homogenous switches and contribution. The traditional reconfigurable switch is proposed in Section II,in which we depict the contrasts among the all the switches are discussed In Section III, we display proposed swapping techniques is discussed with its merits. In Section IV, we display a few associated works and a specific result analysis and finally the conclusions are regarded in Section V.

### **III.Material and methods:**

## A.2D STRUCTURE OF RECONFIGURABLE ROUTING SELECTION STRATEGIES FOR NETWORKS-ON-CHIP

ISSN (PRINT): 2393-8374, (ONLINE): 2394-0697, VOLUME-4, ISSUE-11, 2017

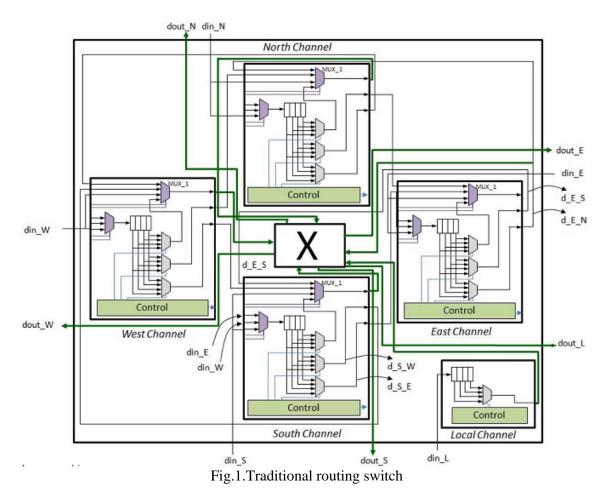

As shown in the Fig.1.The traditional reconfigurable design is equipped for manage execution because of the way that, factually, no longer all supports are utilized the greater part of the time. In this structure the reconfigurable different buffer for each channel is allocated for data storage and communication as shown in the fig.1. In this architecture the new thought makes utilization of more noteworthy multiplexers to permit the reconfiguration framework. As per this figure, each channel has five multiplexers, and two of those multiplexers are responsible to control the enter and yield of records. These multiplexers blessing a fixed length, being autonomous of the buffer estimate. Other three multiplexers are fundamental to represent the examination and compose procedure of the First in first out (FIFO). These multiplexers are overseen by methods for the Finite state machine (FSM) of the FIFO. With a specific end goal to lessen steering and additional multiplexers, we embraced the methodology of changing over the oversee some portion of each direct In final product, each channel needs to perceive its own channel and moreover how a decent arrangement the neighbor channels involve of its own special support set. At that point, based absolutely in this actualities, each channel controls the capacity of its data. [6]

In this format, the Local Channel the utilization of neighboring buffer, just the South, North, West, and East Channel of a switch can make utilizing their abutting channels. Each channel can obtain three information inputs. Give us a chance to recall the South Channel as an occurrence, having the resulting inputs: the possess input (din S), the correct neighbor input (din E), [7] and the left neighbor input (din W). For illustration capacities, enable us to accept we're the utilization of a switch with buffer profundity same to four, and there might be a switch that wants to be configured as takes after: South Channel with support profundity equivalent to 9, East Channel with buffer force equivalent to 2, West Channel with buffer profundity indistinguishable to one, and North Channel with buffer power equivalent to 4. In such case, the South Channel wishes to get support spaces from its neighbor. As the East Channel involves of its four openings, this channel can open two spaces to its neighbor, however and still, after all that, the South Channel regardless needs additional three buffer spaces. As the West Channel involves least complex one opening, the 3 lacking spaces might be loaned toward the South Channel . At the point when the South Channel has a flit spared inside the East Channel, and this flit ought to be despatched to the yield, it's far outperformed from the East Channel toward the South Channel (d E S), thus the flit is on the double sent to the yield of the South Channel (dout S) by utilizing a multiplexer. The South Channel has the accompanying yields: the own one of a kind yield (dout S) and more prominent out-places (d S E and d S W ) to deliver the flits spared in its channel however having a place with neighbor channels Our thought incorporates reconfiguring the channel reliable with the supply of buffers in the channels. In the event new channel power is required, the buffer force is a la mode opening through space, and this alteration is made each time a buffer opening is free. [7-10]For the arrangement of benchmarks utilized as a part of this canvases, and as said in bunches of related works, at whatever point the application is changed, an extraordinary transfer speed is required some of the channels. The reconfigurable switch can exchange its power in handiest couple of cycles, which implies a little execution overhead. In addition, as each center sends bundles at an outstanding charge, the reconfiguration of the switch was implemented that in some attainable period slack. As the traffic is made out of parcels, the buffers aren't utilized a 100% of the time in all parts of the group. In this architecture the parameters such as area overhead and delay are high which leads to improve the complexity of the architecture which can be optimized through swapping technique as discussed below.[11-15]

### **B.2D STRUCTURE OF SWAPPING ROUTING SELECTION STRATEGIES FOR NETWORKS-ON-CHIP**

Runtime Contention and Bandwidth-Aware Adaptive Routing Selection Strategies for Networks-on-Chip. This method helps to increase reliability of Network-on-chip by avoiding errors and crosstalk between the routers.Whereas this methodpresents the design of a NoC router based on turn model. A swapping router is used to avoid deadlock conflicts. Also the router integrates a dynamic arbiter to increase the Quality of Service of network.[16-18]

Router Parameters2D routerBuffer Depth4Flit size (bit)32

| Switching     | wormhole<br>Credit based |  |

|---------------|--------------------------|--|

| Flow control  |                          |  |

| Scheduling    | Dynamic arbiter          |  |

| Routing       | swapping router          |  |

| Target device | Virtex5 XC5VFX70T        |  |

| - mi i i      | 1 1 6 4 1 1              |  |

The arbiter module of the switch allocator uses a round-robin and a priority scheduler schemes to assign the highest priority packet to the adequate output port. The turn modelwhich is a deadlock-free swapping router for mesh NoC.In wormhole switching, the deadlock situation occurs when packets are waiting for each other in cyclic dependencies. In 2D mesh network, routers may forward packets in four directions: North, East, South and West. As shown in figure 3.b, packets may take eight turns for each direction. A turn in this context refers to a change of 90-degree of the travelling direction of the packet. The swapping router is chosen due to its scalability and simplicity. Further "Design of Low Power & Reliable Networks on Chip through Joint Crosstalk Avoidance and Multiple Error Correction Coding "Crosstalk Avoiding Double Error Correction Scheme encoder is a simple combination of Hamming coding followed by DAP or BSC encoding to provide protection against cross talk.

- **Boundary Shift Coding (BSC)** is achieved by avoiding a shared boundary between two successive code words.

- The Duplicate Add Parity (DAP) scheme achieves joint crosstalk avoidance and single error correction

capability by duplicating each bit of the n-bit flit and placing the copies adjacent to each other to avoid crosstalk, and by also computing a parity bit from the initial bits to enable single error correction.[19-20]

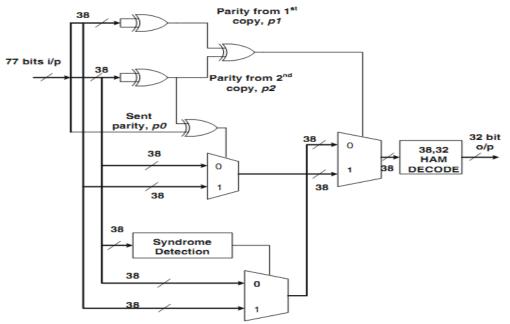

**The decoding algorithm** consists of the following simple steps:

1. The equality bits of the individual Hamming duplicates are ascertained and contrasted and the sent equality;

2. If these two equalities acquired in stage 1 contrast, at that point the copy whose equality matches with the transmitted equality is chosen as the yield copy of the principal arrange.

3. If the two equalities are equivalent, at that point any one duplicate is sent forward for disorder recognition.

4. If the disorder got for this duplicate is zero then this duplicate is chosen as the yield of the router. Something else, the substitute duplicate is chosen.

5. The yield of the primary stage is sent for (38, 32) single mistake adjusting Hamming translating, at last creating the decoded CAD EC yield. As shown in the fig.2.

Figure.1.Block structure of CADEC output

#### INTERNATIONAL JOURNAL OF CURRENT ENGINEERING AND SCIENTIFIC RESEARCH (IJCESR)

The reconfigurable transfer lets the proposed swapping method outperforms existing reconfigurable router design in terms of area overhead and timing constrain.

### **IV.Results and discussion:**

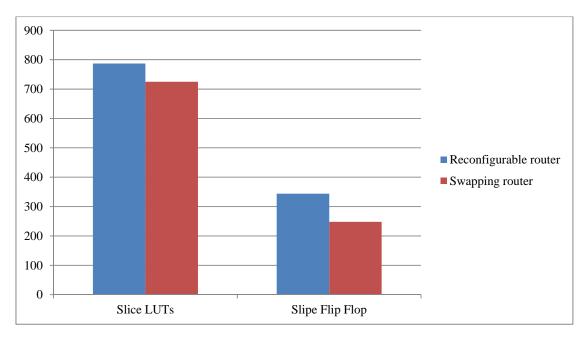

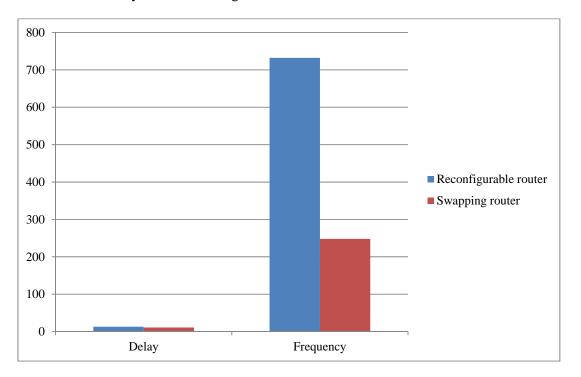

Proposed swapping approach improves the logic circuit's throughput while reducing some of the overheads in the existing method. In this architecture the cycle time overhead of **Table 1** Logic utilization of device

traditional reconfigurable switches avoided as there are no internal buffer. Cycle time is obtained by the variation in the signal propagation delay from the logic and delays from the register of input and output. Latency from the pipeline avoids the traditional method overhead because the signals do not propagate from end to end of internal buffer. Overhead due to partitioning is reduced as the pipeline is not divided into stages separated by buffer.

|                  | Reconfigurable Router | Swapping Router |

|------------------|-----------------------|-----------------|

| Slice LUTs       | 787                   | 725             |

| Slice Flip Flops | 344                   | 248             |

| Delay            | 13.14ns               | 11.608ns        |

| Frequency        | 732.224MHz            | 86.149MHz       |

It explores the idea of pipelining approach which in turn reduces the Delay with High operating Frequency and High Throughput of the device in future as shown in the Fig.4. Redundancy has reduced through this reconfigurable swapping architecture through parallel pipeline approach. The optimized results are shown in table.1.In the above result the total composition of look up table has been given in detail, in turn helps to analyze the utilization of bit in the memory of the particular device which has selected for implementation. In case partitioning makes registers of considerably bigger width to be essential then the decline in the combinational delay per stage will be offset by the rise in the completion delay so that the throughput of the system may not essentially rise; then in order to reduce the delay and to improve throughput parallel pipeline stage approach is taken.

### Fig.3. Comparison of area overhead constrains

### A. Area report comparison

Area report has analyzed for all the methods which includes (As shown in Table 4.1).An n-bit LUT can code any Boolean function of ninput by designing of functions as truth tables. This is a best way of Boolean logic functions encoding, and LUTs with 4-6 bits of input are in fact the important constituent of modern FPGAs. Storage caches (such as processor caches for either data or code or disk caches for files) work also like a lookup table. As shown in the Fig.3.

### V. Conclusion

The authors have arranged a novel swapping router based method to be implemented in equipment of gradable routing switches. The proposed authority show for H-NoC plan is adaptable; it offers standard on-chip correspondence foundation for interneuron property, and a spike movement pressure system to decrease activity overhead. The arranged H-NoC outline switch configuration to the RTLlevel execution reenactments utilizing a major assortment simulated spike activity of circumstances. Recreation comes about exhibit that the arranged H-NoC approach offers a high, fundamental execution in wording region, postponement and worldly request. Results are promising that the reconfigurable transfer lets the proposed swapping method outperforms existing reconfigurable router design in terms of area overhead and timing constrain.

### **References:**

1. Gao, M., & Kozyrakis, C. (2016, March). HRL: efficient and flexible reconfigurable logic for near-data processing. In High Performance Computer Architecture (HPCA), 2016 IEEE International Symposium on (pp. 126-137). Ieee.

- George, S., Kim, S., Shah, S., Hasler, J., Collins, M., Adil, F., ... & Ramakrishnan, S. (2016). A programmable and configurable mixed-mode FPAA SoC. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 24(6), 2253-2261.

- Annoni, A., Guglielmi, E., Carminati, M., Grillanda, S., Ciccarella, P., Ferrari, G., ... & Morichetti, F. (2016). Automated routing and control of silicon photonic switch fabrics. IEEE Journal of Selected Topics in Quantum Electronics, 22(6), 169-176.

- Stabile, R., Albores-Mejia, A., Rohit, A., & Williams, K. A. (2016). Integrated optical switch matrices for packet data networks. Microsystems & Nanoengineering, 2, 15042. [2] M.

#### INTERNATIONAL JOURNAL OF CURRENT ENGINEERING AND SCIENTIFIC RESEARCH (IJCESR)

Azimi, N. Cherukuri, D. N. Jayasimha, A. Kumar, P. Kundu, S. Park, I. Schoinas, and A. S. Vaidya, "Integration challenges and

tradeoff for tera-scale architectures," Intel Technol. J., vol. 11, no. 3,Aug. 2007.

- 5. L. Manferdelli, N. K. Govindaraju, and C. Crall, "Challenges and op-portunities in many-core computing," Proc. IEEE, vol. 96, no. 5, pp.808–815, May 2008.

- J. Andrews and N. Baker, "Xbox 360 system architecture," IEEE Micro, vol. 26, no. 2, pp. 25–37, Mar./Apr. 2006.

- M. Vestias and H. Neto, "Area and performance optimization of ageneric network-on-chip architecture," in Proc. Symp. Integr. CircuitsSyst. Des. (SBCCI), 2006, pp. 68–73.

- Stabile, R., Albores-Mejia, A., Rohit, A., & Williams, K. A. (2016). Integrated optical switch matrices for packet data networks. Microsystems & Nanoengineering, 2, 15042.

- Annoni, A., Guglielmi, E., Carminati, M., Grillanda, S., Ciccarella, P., Ferrari, G., ... & Morichetti, F. (2016). Automated routing and control of silicon photonic switch fabrics. IEEE Journal of Selected Topics in Quantum Electronics, 22(6), 169-176.

- Yang, L., Xia, Y., Zhang, F., Chen, Q., Ding, J., Zhou, P., & Zhang, L. (2015). Reconfigurable nonblocking 4-port silicon thermo-optic optical router based on Mach–Zehnder optical switches. Optics letters, 40(7), 1402-1405.

- Chen, M., Zhang, Y., Hu, L., Taleb, T., & Sheng, Z. (2015). Cloud-based wireless network: Virtualized, reconfigurable, smart wireless network to enable 5G technologies. Mobile Networks and Applications, 20(6), 704-712.

- Liu, X., Mao, M., Liu, B., Li, H., Chen, Y., Li, B., ... & Yang, J. (2015, June). RENO: A high-efficient reconfigurable neuromorphic computing accelerator design. In Design Automation Conference (DAC), 2015 52nd ACM/EDAC/IEEE (pp. 1-6). IEEE.

- 13. Zilberman, N., Watts, P. M., Rotsos, C., & Moore, A. W. (2015). Reconfigurable

network systems and software-defined networking. Proceedings of the IEEE, 103(7), 1102-1124.

- 14. Li, Z., Zhang, M., Wang, D., Xie, D., Cui, Y., & Yang, Q. (2017, March). Demonstration of reconfigurable WDM multicast supporting content replication and protection switching for content delivery optical network. In Optical Fiber Communications Conference and Exhibition (OFC), 2017 (pp. 1-3). IEEE.

- 15. Roorda, P. D., & McLaughlin, S. (2017). U.S. Patent No. 9,548,834. Washington, DC: U.S. Patent and Trademark Office.

- 16. Baskar, S., & Saravanan, M. (2012). Error detection and correction enhanced decoding of differenceset codes for memory application. International Journal of Advanced Research in Computer and Communication Engineering, 1(10), 816-820.

- 17. Hadimani, H. C., Latte, M. V., Tejomurthy, P. H. S., Dhulipala, V. S., & Baskar, S. (2016, February). Optimized mathematical model for cell receivers running in spatially problematic multi path channels for wireless systems in smart antennas. In Emerging Trends in Engineering, Technology and Science (ICETETS), International Conference on (pp. 1-7). IEEE.

- Baskar, S., & Dhulipala, V. R. (2016). Comparative Analysis on Fault Tolerant Techniques for Memory Cells in Wireless Sensor Devices. Asian Journal of Research in Social Sciences and Humanities, 6(cs1), 519-528.

- Baskar, S. (2014, March). Error recognition and correction enhanced decoding of hybrid codes for memory application. In Devices, Circuits and Systems (ICDCS), 2014 2nd International Conference on (pp. 1-6). IEEE.

- 20. Baskar, S., & Dhulipala, V. S. RELIABILITY ORIENTED PLACEMENT AND ROUTING ANALYSIS IN DESIGNING LOW POWER MULTIPLIERS.