### THD ANALYSIS OF 21-LEVEL THREE PHASE CASCADED H-BRIDGE MULTI-LEVEL INVERTER WITH DIFFERENT MULTI-CARRIER LEVEL SHIFT PWM TECHNIQUES

V. Ramu<sup>1</sup>, P.Shiva Sai Sagar<sup>2</sup> <sup>1</sup>Assistant Professor, University College of Engineering, Kakatiya University, Kothagudem <sup>2</sup>B.Tech Student, University College of Engg, Kothagudem

#### Abstract

Nowadays, the industries demanding more power with low harmonics for the high power Thus Multilevel applications. Inverter concept has been introduced. The concept of the Multilevel Inverters becoming more popular for the high power applications due to less harmonics and high power ratings. The importance of the multilevel converters has been increased since the last decade. Several topologies have been implemented, amongst these topologies, the Cascaded Hbridge Multilevel Inverter is proposed. Cascaded MLI are ideal for connecting renewable energy sources with an AC grid. Even though the number of modulation techniques are available for controlling the multilevel inverter but, MULTI-

## CARRIER LEVEL-SHIFT PULSE WIDTH MODULATION

**TECHNIQUES** are frequently used due to its simplicity and easy implementation. In this paper simplified simulation modelling of various multi-carrier level-shift **PWM** techniques (such as PID, PO, & APOD) are proposed for n-level generation. The proposed modulation techniques are explained for '21-LEVEL THREE PHASE **CASCADED H-BRIDGE**

(CHB)'. The simulation of the modulation techniques is set up in MATLAB/Simulink. And an analysis has been made on calculating percentage THD for different multi-carrier levelshift PWM techniques.

Key words: multilevel inverter, cascaded Hbridge, multicarrier (MC) level shift pulse

# width modulation techniques, PID, PO, APOD and THD.

**I.INTRODUCTION**

Multilevel inverters are becoming more popular as they have tremendous advantages such as low harmonic distortion, improved power quality, reduced voltage stress across the switches, less electromagnetic interference and reduction in the filter size. The three basic topologies of multilevel inverter are the diode clamped, capacitor clamped and Cascaded Hbridge (CHB) multilevel inverter [1].Among these, a survey on CHB [2] has been done and concluded that it has become an attractive topology due to its modularity and simplicity to control.

Pulse width modulation (PWM) techniques play vital role in order to get the desired output in multilevel inverters,. Several modulation techniques have been proposed and introduced in the literature such as: selective harmonic elimination PWM (SHE-PWM), space vector PWM, sinusoidal PWM (SPWM), third harmonic injected PWM (THPWM), 60° modulated sinusoidal PWM (SDPWM) and trapezoidal PWM (TRPWM)

(SVPWM) and multi-carrier PWM (MCPWM). The main challenge associated with the SHE-PWM and SVPWM techniques is, complexity in calculations in multilevel inverter above 5-levels. Different PWM techniques having their own advantages and disadvantages.

The MCPWM technique is the most widely used and well accepted because it is the simplest technique to generate multilevel pulses to control individual power switches for any output level inverters by comparing reference signal with triangular signals. The broad classification of multicarrier PWM is based on types of carrier signals and modulating signals. There are five well known carrier signals and are classified as level shifted or vertical shifted signals and phase shifted or Horizontal shifted signal namely; phase disposition (PD), phase opposition and disposition (POD), alternate phase opposition disposition (APOD) and phase shifted (PS) PWM can be used to implement any type of inverters. Recently, in number of literature, authors have proposed the method to mitigate the CHB power balancing problem using level shifted PWM techniques only.

SPWM is the commonly used reference signal due to its simplicity to generate it. THPWM, SDPWM and TRPWM reference signals are used where linear modulation is required by flattening the top of these reference signals. Carrier signals and modulating signals both provides freedom in amplitude, frequency and phase. So based on combination of carrier signals and modulating signals, number of multilevel PWM output can be generated [5].

The main aim of this paper is to present a simplified way to generate simulation model for various multi-carrier levelshift PWM techniques and their performance analysis based on total harmonic distortion (THD) for 21-level three phase CHB inverter. The generation of various multi-carrier levelshift PWM techniques will be same for any multilevel inverters. The simulation results in MATLAB/SIMULINK platform. The paper is organized as follows

Section II-provides an overview of CHB (single cell). Section III-Describes 21-level 3-phase CHB MLI & its connection diagram.

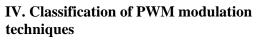

Section IV- Classification of PWM modulation techniques. Section V &VI-Theoretical method to develop various carrier signals and modulating signal.

Section VII- Generation of control pulses for inverter

Section VIII- Simulation results

Section IX- Conclusion of the work is summarized. Section X-Future scope.

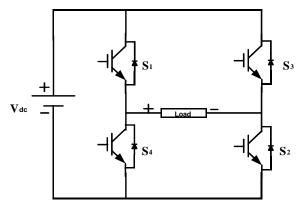

#### II.CASCADED H-BRIDGE INVERETER ( Single-cell )

A single-phase structure of a three level cascaded inverter is illustrated in Figure 1. Each H - bridge

inverter cell, can generate three different voltage outputs, +Vdc, 0, and –Vdc by connecting the dc source to the ac output by different combinations of the four switches, S<sub>1</sub>, S<sub>2</sub>, S<sub>3</sub>, and S<sub>4</sub>. To obtain +Vdc, switches S<sub>1</sub> and S<sub>2</sub> are turned on, whereas –Vdc can be obtained by turning on switches S<sub>3</sub> and S<sub>4</sub>. By turning on S<sub>1</sub> and S<sub>3</sub> or S<sub>2</sub> and S<sub>4</sub>, the output voltage is 0. The ac outputs of each of the different full-bridge inverter levels are connected in series such that the synthesized voltage waveform is the sum of the inverter outputs. The number of output phase voltage Levels n in a cascade inverter is defined by n = 2h+1, where h is the number of H-bridges to which a separate dc source is connected. [5].

| Switches turn on | Voltage level |

|------------------|---------------|

| S1,S2            | + Vdc         |

| \$3,\$4          | - Vdc         |

| S1,S3            | 0             |

#### Fig.1 single cell of CHB III.21-level 3-phase CHB MLI

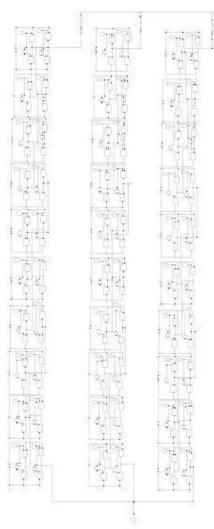

In this, each individual phase of 21-level 3-phase cascaded MLI constitutes ten cascaded H-cells. (All the ten Hcells are connected in series). The ac outputs of each of the different full-bridge inverter levels are connected in series such that the synthesized voltage waveform is the sum of the each inverter (H-cell) output.

The number of output phase voltage levels (n) in a cascade inverter is defined by n = 2h+1, where **h**-is the number of Separate dc sources & **n**- is number of output voltage levels.

Therefore, for n=2(10) + 1=21 levels. Each phase produces 21-levels of output through 10 H-cells connected in series with low THD.Figure-2 shows Connection diagram of 3-phase CHB MLI (21-levels).

Fig.2 Three phase 21-level cascaded MLI

As said earlier (section-I), the main challenge associated with the SHE-PWM and SVPWM techniques is, complicated calculation required to control multilevel inverter above 5levels. The MCPWM technique is the most widely used and well accepted because it is the simplest technique to generate multilevel pulses to control individual power switches for any output level inverters by comparing reference signal with triangular signals[3].

#### MULTI-CARRIER PWM (MCPWM) SCHEMES

To control and to generate high quality output waveform of multilevel converter, an appropriate modulation schemes is required. Among these modulation techniques, an important family of modulation technique, MCPWM stands out because it offers significant simplicity and easy to implement switching Waveforms [3].

Multi-carrier PWM is broadly classified as two types

- 1. Multi-carrier level shift PWM

- A. Phase in-phase disposition (PID).

- B. Phase opposition disposition (POD).

- C. Alternative phase opposition disposition (APOD).

- 2. Multi-carrier phase shift PWM

But, the problem encountered with multi-carrier phase shift PWM is that, it shows a little worse line to line voltage THD profile compared to Multi-carrier level shift PWM techniques [4].

Hence, in order to obtain lower THD, here Multi-carrier level shift PWM techniques are used and are implemented on three-phase 21level cascaded MLI.

#### V .Multi-carrier Level Shifted PWM (MCLS-PWM)

In the MCLS-PWM methods all the carrier signals use triangular signals, cover the total extent range of generated converter output voltage and consist same amplitude and frequency. They are classified basically based on the placement of various carrier signals [3].

For generation of n level, n-1 carrier signals are required.

For generation of 21 level, 21-1=20 carrier signals are required

The MCLS-PWM methods are used in the controlling of inverters where power balancing is not required [3]. Here all the multi-carrier level-shifted PWM techniques are shown for R-phase.

(Similarly these methods are carried out for Y & B phases respectively).

#### A. Phase in-phase Disposition PWM (PID-PWM)

In this technique all the carrier waves are selected with same phase and magnitude. This technique compares a reference sinusoidal wave with multiple triangular carrier waves to generate the switching pulses. For an n-Level inverter, (n-1) carrier signals are used [1].

**Fig.3** Method to generate PID-PWM carrier & reference signals for R-phase.

Above fig.3 shows the one phase(R-PHASE) arrangement of reference and carrier waveforms to generate switching pulses for the 21- level cascaded multi-level inverter for PIDPWM technique. Likewise PID-PWM is carried out for B, Yphases respectively.

The reference sinusoidal waveform having peak to peak amplitude of 'A<sub>m</sub>' and frequency of 'f<sub>m</sub>' is compared with every carrier signal. The carrier signals are of the same frequency 'f<sub>c</sub>' and same amplitude 'A<sub>c</sub>'. The zero amplitude is concentrated in the middle of the carrier set. If the amplitude of the reference wave is greater than the amplitude of the carrier signal, then the corresponding switch is turned ON. For a CHB multilevel inverter the amplitude modulation index M<sub>I</sub> is defined as

"The ratio of amplitude of reference wave  $(A_m)$  to the amplitude of carrier wave  $(A_c)$ " & is given by

$$M_{I} = (A_{m})/(A_{c})^{2}$$

The frequency ratio (Mf) is defined as

"The ratio of carrier frequency (f-car) to the reference frequency (f-mod)" & is given by

#### $M_{f}=(f_{c})/(f_{m})$

The inverter gives a zero state output when the sinusoidal signal is lesser than the upper carrier signal but more than the lower carrier wave. When the reference signal is less than first lower carrier wave, the inverter is switched to -1 (-Vdc - state) stage [1]. When the reference signal is higher than first upper carrier wave, the inverter is switched to +1 (+Vdc - state) stage. Likewise all ac outputs of each of the different cascaded H-Bridge inverters in each phase (R, Y, B) are connected in series such that the synthesized voltage waveform is the sum of the each inverter (H-cell) output.

#### 2. Phase Opposition Disposition PWM (POD-PWM )

In case of POD-PWM technique, the carrier signals above the zero axes and below the zero axes are 180° out of phase but the carriers above the zero axes or positive carrier signals are in same phase and the carriers below the zero axes or negative carrier signals are in same phase [3].

#### Fig.4 Method to generate PO-PWM

Method to generate PO-PWM carrier & reference signals for R-phase is shown in fig.4 shows the arrangement of single phase (R-PHASE) reference and carrier waveforms to generate switching pulses for the 21- level cascaded multilevel inverter for POD-PWM technique. Likewise PO-PWM is carried out for B, Y-phases respectively.

#### 3. Alternate Phase Opposition Disposition PWM ( APODPWM )

In this method, the entire carrier signals are alternate  $180^{\circ}$  shifted with its neighbor is

demonstrated i.e. each carrier of this method is phase shifted by 180 degrees from its adjacent carrier [3]. Below fig.5 shows the one phase (R-PHASE) arrangement of reference and carrier waveforms to generate switching pulses for the 21- level cascaded multi-level inverter for APOD-PWM technique. Likewise APOD-PWM is carried out for B, Y-phases respectively.

**Fig.5** Method to generate APOD-PWM carrier & reference signals for R-phase.

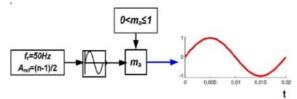

#### VI. MODULATION SIGNAL (REFERENCE SIGNAL) Sinusoidal PWM

The pure sinusoidal signal used with carrier signals is known as SPWM, & is illustrated in below fig.6 [3]. Likewise three-phase sine-wave modulation signals are generated with their respective phase-shifts i.e. R phase - 0degrees, Y phase120degrees, B phase-240degrees (-120degrees) respectively. It is the widely used method in number of applications due to its simplicity.

**Fig.6** Modulation signal for R-phase

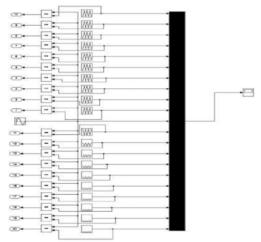

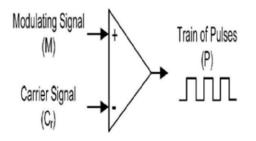

VII. GENERATION OF MULTI-

**CARRIER SIGNALS (control pulses)** The control diagram of generating train pulses is shown in below fig7. The modulating signal of each phase is compared with the carrier signals at each instant. If the modulating signal is greater than zero with the positive carriers then it will generate '1' otherwise '0' and if the modulating signal is greater than zero with the negative carriers then it will generate '-1' otherwise '0' [3].

Fig.7 Control diagram to generate train of pulses

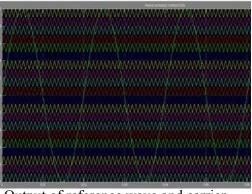

**Fig.8** Output of reference wave and carrier waves for PID- PWM (21-level) of R-phase

**Fig.9** Output of reference wave and carrier waves for PO-PWM (21-level) of R-phase.

| EV/ODD00000 | www.wwwwww |         |            |

|-------------|------------|---------|------------|

| MAAAAAAAAA  |            | www.www | www.www.ww |

|             |            |         |            |

|             | mmmm       |         |            |

|             |            |         |            |

|             | www.www    | www.www | MANA MANA  |

|             |            |         |            |

| MMMMMM      |            |         |            |

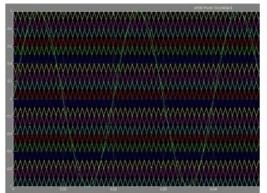

**Fig.10** Output of reference wave and carrier waves For APOD-PWM (21-level) of R-phase.

#### VIII. SIMULATION RESULTS

To analyze the proposed simplified method to generate MULTI-CARRIER LEVEL-SHIFT PWM techniques have been theoretical discussed. These multi-carrier level-shifted modulation techniques, have been conducted on 21-level three phase CHB inverter having equal voltage sources of 10V, R-L (R=10 $\Omega$  & L=5mH) load, with fundamental reference frequency of 50Hz, carrier-frequency of 1050Hz (i.e. 21x50) and modulation index of (ma) 1 & 0.95. The MATLAB/Simulink software platform is utilized for simulation.

The variation of harmonic distortion with modulation index & Line voltages THD have been drawn for various multi-carrier level shift PWM techniques for three phase 21level MLI & are as follows

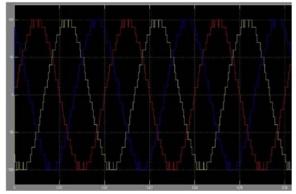

#### 1. Phase in-phase Disposition PWM (PID-PWM)

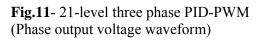

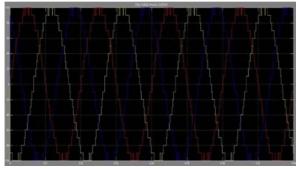

**Fig.12**- 21-level three phase PID-PWM Line output voltage waveform.

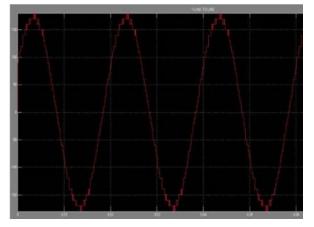

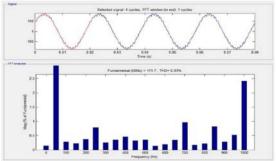

**Fig.13**- PID-PWM--FFT-Analysis (harmonic spectrum)

| Samplin |      | i me    | Se-05  |       |        |        |

|---------|------|---------|--------|-------|--------|--------|

| Samples | per  | cycle = | 400    |       |        |        |

| DC comp | oner | nt =    | 0.1718 | 1     |        |        |

| Fundame | ntal | L =     | 171.8  | peak  | (121.5 | Ims)   |

| THD     |      | -       | 4.778  |       |        |        |

| 0       | Hz   | (DC) :  |        | 0.1   |        | 270.0* |

| 50      | Hz   | (Fnd):  |        | 100.0 |        | 29.3*  |

| 100     | Hz   | (h2):   |        | 0.2   | 0.     | -89.5" |

| 150     | Hz   | (h3):   |        | 0.2   | 8 8    | 226.8" |

| 200     | Hz   | (h4):   |        | 0.2   | 08     | -89.0* |

| 250     | Hz   | (h5):   |        | 0.8   |        | -41.7° |

| 300     | Hz   | (h6):   |        | 0.2   |        | -88.7* |

| 350     | Hz   | (h7):   |        | 0.3   | 1.5    | 18.9°  |

| 400     | Hz   | (h8) :  |        | 0.2   |        | -88.5" |

| 450     | Hz   | (h9):   |        | 0.3   | 8 %    | 264.8" |

| 500     | Hz   | (h10):  |        | 0.2   |        | -88.3* |

| 550     | Hz   | (h11) : |        | 0.1   | 1.6    | 256.2" |

| 600     | Hz   | (h12):  |        | 0.2   | 0 %    | -88.1" |

| 650     | Hz   | (h13):  |        | 0.8   | 2.8    | -64.2" |

| 700     | Hz   | (h14):  |        | 0.2   |        | -87.8" |

| 750     | Hz   | (h15):  |        | 0.2   | 4.     | -75.7* |

| 800     | Hz   | (h16):  |        | 0.2   |        | -87.6" |

| 850     | Hz   | (h17):  |        | 0.7   | 0.5    | -57.0° |

Fig.14- PID-PWM--FFT-for Ma=1

2. Phase Opposition Disposition PWM (POD-PWM)

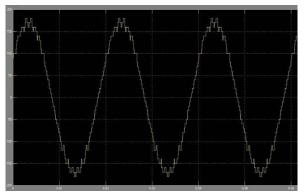

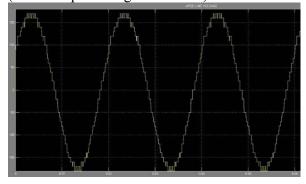

Fig.15- 21-level three phase POD-PWM (Phase output voltage waveform).

**Fig.16-** 21-level three phase POD-PWM (Line output voltage waveform)

#### INTERNATIONAL JOURNAL OF CURRENT ENGINEERING AND SCIENTIFIC RESEARCH (IJCESR)

**Fig.17** POD-PWM--FFT-Analysis (Harmonic spectrum)

| Samplin |      |         |   | 5e-05 |       |      |         |

|---------|------|---------|---|-------|-------|------|---------|

| Samples | per  | cycle : | = | 400   |       |      |         |

| DC comp | oner | nt a    | = | 0.246 | 7     |      |         |

| Fundame | ntal | L .     | - | 171.7 | peak  | (121 | .4 rms) |

| THD     |      |         | = | 6.03% |       |      |         |

| 0       | Hz   | (DC):   |   |       | 0.1   | 49   | 270.0*  |

| 50      | Hz   | (Fnd) : |   |       | 100.0 | .00  | 29.1"   |

| 100     | Hz   | (h2):   |   |       | 0.2   | .8%  | -62.4°  |

| 150     | Hz   | (h3):   |   |       | 0.2   | 3%   | 237.7°  |

| 200     | Hz   | (h4):   |   |       | 0.3   | 88   | -18.8*  |

| 250     | Hz   | (h5):   |   |       | 0.7   | 8.   | -47.0"  |

| 300     | Hz   | (h6):   |   |       | 0.2   | 5%   | 261.5°  |

| 350     | Hz   | (h7):   |   |       | 0.3   | 5.   | -18.1°  |

| 400     | Hz   | (h8):   |   |       | 0.4   | 68   | -62.6"  |

| 450     | Hz   | (h9):   |   |       | 0.3   | 28   | 269.3*  |

| 500     | Hz   | (h10):  |   |       | 0.3   | 15%  | 247.0°  |

| 550     | Hz   | (h11):  |   |       | 0.1   | .3%  | 224.7°  |

| 600     | Hz   | (h12):  |   |       | 0.1   | .9%  | 234.7°  |

| 650     | Hz   | (h13):  |   |       | 0.3   | 48   | -54.0*  |

| 700     | Hz   | (h14):  |   |       | 0.5   | 7%   | 146.6°  |

| 750     | Hz   | (h15):  |   |       | 0.1   | .78  | -54.2°  |

| 800     | Hz   | (h16):  |   |       | 0.2   | 28   | -66.1"  |

| 850     | Hz   | (h17):  | _ |       | 0.8   | 25   | -60.8°  |

Fig.18 POD-PWM--FFT-for Ma=1 3. Alternate Phase Opposition Disposition PWM (APODPWM)

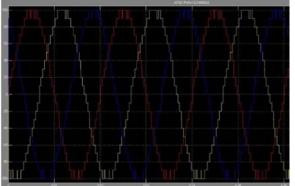

**Fig.19-**21-level three phase APOD-PWM (Phase output voltage waveform)

**Fig.20**- 21-level three phase APOD-PWM (Line output voltage waveform)

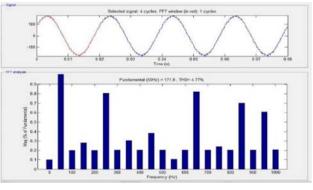

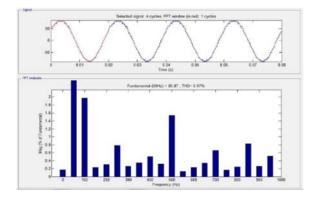

Fig.21 APOD-PWM-FFT-Analysis for Ma=1

| Samplin |      |        |   |        |      |        |        |

|---------|------|--------|---|--------|------|--------|--------|

| Samples | per  | cycle  | = | 400    |      |        |        |

| DC comp | oner | t      | = | 0.1483 | £    |        |        |

| Fundame | ntal |        | - | 85.87  | peak | (60.72 | 2 rms) |

| THD     |      |        | = | 5.97%  |      |        |        |

| 0       | Hz   | (DC) : |   |        | ο.   | 17%    | 270.0  |

| 50      | Hz   | (Fnd)  | 2 |        | 100. | 00%    | 29.1   |

| 100     | Hz   | (h2):  |   |        | 1.   | 97%    | 152.8  |

| 150     | Hz   | (h3) : |   |        | 0.   | 23%    | 237.7  |

| 200     | Hz   | (h4) : |   |        | 0.   | 31%    | -14.6  |

| 250     | Hz   | (h5):  |   |        | 0.   | 78%    | -47.0  |

| 300     | Hz   | (h6) : |   |        | 0.   | 25%    | -84.5  |

| 350     | Hz   | (h7):  |   |        | ο.   | 35%    | -18.1  |

| 400     | Hz   | (h8):  |   |        | 0.   | 50%    | -54.6  |

| 450     | Hz   | (h9):  |   |        | 0.   | 32%    | 269.3  |

| 500     | Hz   | (h10): |   |        | 1.   | 54%    | 12.4   |

| 550     | Hz   | (h11): |   |        | 0.   | 13%    | 224.7  |

| 600     | Hz   | (h12): |   |        | 0.   | 23%    | -78.6  |

| 650     | Hz   | (h13): |   |        | 0.   | 34%    | -54.0  |

| 700     | Hz   | (h14): |   |        | 0.   | 66%    | -73.3  |

| 750     | Hz   | (h15): |   |        | 0.   | 178    | -54.2  |

| 800     | Hz   | (h16): |   |        | 0.   | 24%    | -18.9  |

| 850     | Hz   | (h17): |   |        | 0.   | 82%    | -60.8  |

Fig.22 APOD-PWM--FFT-for Ma=1

| MC-<br>LEVELSHIFT-<br>PWM<br>TECHNIQUE | THD%<br>MODULATION<br>INDEX=0.95 | THD%<br>MODULATION<br>INDEX=1 |

|----------------------------------------|----------------------------------|-------------------------------|

| PID-PWM                                | 4.89%                            | 4.77 %                        |

| TECHNIQUE                              |                                  |                               |

| POD-                                   | 6.58%                            | 6.03%                         |

| PWM                                    |                                  |                               |

| TECHNIQUE                              |                                  |                               |

| APOD-                                  | 5.64%                            | 5.97%                         |

| PWM                                    |                                  |                               |

| TECHNIQUE                              |                                  |                               |

| TARLE 1                                | •                                | •                             |

#### TABLE-1

#### IX. Conclusion

In this paper, simplified method to generate simulation model for multi-carrier LEVEL-SHIFT PWM techniques were presented. These MC-LEVEL SHIFT PWM techniques for CHB inverter were analyzed with a prevailing

MATLAB/simulation tool. The simplified method is valid for n-level generation. Multicarrier level shift pulse width modulated cascaded H-bridge converter is simulated for 21level. The principle of the MC-LEVEL-SHIFT-PWM has been verified by simulation result. In order to analyze the THD performance of line voltage among the various level shift modulation technique, comparison has been done.

From these figures (11 to 22) & table-1 it is clear that the "Phase in Phase Disposition (PID) method" of Multi Carrier level shift pulse width Modulation is better than other Modulation techniques. These have low THD (4.7%) and better voltage (121.5 R.M.S). Phase In-phase deposition (PID) level shifted modulation strategy provides the best line to line voltage THD profile among other level shifted and phase shifted multi carrier pulse width modulation techniques

#### **X. FUTUREWORK**

In order to meet now a day's load demand, along with the generation of electrical energy from conventional energy sources we also have to go for non conventional energy sources of generation of electricity. Therefore now a days Distributed Generating Stations are going to be installed at the load centers especially in villages for which in most of the cases the source of electricity is solar energy. Generally the voltage generated from each PV Cell is around only 12 to 24 volts. There we require DC-DC boost converters to step up the voltage first and then it should be converted from DC to AC with the help of multilevel inverters. But as the number of levels from the cascaded H-bridge is increased then there will not be any need of DC-DC boost converter. Directly individual PV cell is connected to each H-bridge in cascaded multilevel inverter. This is the major advantage of cascaded H-bridge multilevel inverters with increased number of levels.

#### References

2014.

[1]-Pratikaprajapatit, Meenakshi Jayaraman, Sreedevi V.T– "Harmonic Elimination in A Five Level Multilevel Inverter"2016 International Conference on Computer Communication and Informatics (ICCCI-2016), Jan. 07 - 09, 2016, Coimbatore, India.

[2]-Mariusz Malinowski, K.Gopakumar, Jose Rodriguez-"A Survey on Cascaded Multilevel Inverters"- 2010 IEEE Transactions on Industrial Electronics-Volume-57. Issue-7. [3]-Rekha Agrawal, Jitendra Kumar tandekar, Shailendra Jain-"Multi-Carrier Pulse Width Modulation Schemes for Multilevel Converters"- 2016 IEEE Students' Conference on Electrical, Electronics and Computer Science. [4]- Ehsan Taslimi Renani, Mohammad Fathi Mohammad Elias, N. A. Rahim-"Performance evaluation of multicarrier PWM methods for cascaded H-Bridge multilevel inverter"UM Power Energy Dedicated Advanced Centre (UMPEDAC), Level 4, Wisma R&D, UM, Jalan Pantai Baharu, 59990 Kuala Lumpur, Malaysia. [5]- K.L.Dheeraj, M.Diwakar, M.DurgaRaj, M.Eswar, K.Naga Venkatesh-"THD Analysis of Cascaded MLI for Various PWM Techniques"international journal of engineering trends And technology (IJETT)-Volume-11 number 3-May